| ||

The Platform Controller Hub (PCH) is a family of Intel microchips, introduced circa 2008. It is the successor to the previous Intel Hub Architecture, which used a northbridge and southbridge instead, and first appeared in the Intel 5 Series.

Contents

- Overview

- Phase out

- Ibex Peak

- Issues

- Langwell

- Tiger Point

- Topcliff

- Cougar Point

- Whitney Point

- Panther Point

- Cave Creek

- Patsburg

- Coleto Creek

- Lynx Point

- Wellsburg

- Sunrise Point

- References

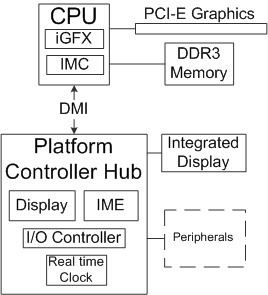

The PCH controls certain data paths and support functions used in conjunction with Intel CPUs. These include clocking (the system clock), Flexible Display Interface (FDI) and Direct Media Interface (DMI), although FDI is only used when the chipset is required to support a processor with integrated graphics. As such, I/O functions are reassigned between this new central hub and the CPU compared to the previous architecture: some northbridge functions, the memory controller and PCI-e lanes, were integrated into the CPU while the PCH took over the remaining functions in addition to the traditional roles of the southbridge.

Overview

The PCH architecture supersedes Intel's previous Hub Architecture, with its design addressing the eventual problematic performance bottleneck between the processor and the motherboard. Over time, the speed of CPUs kept increasing but the bandwidth of the front-side bus (FSB) (connection between the CPU and the motherboard) did not, resulting in a performance bottleneck.

Under the Hub Architecture, a motherboard would have a two piece chipset consisting of a northbridge chip and a southbridge chip. As a solution to the bottleneck, several functions belonging to the traditional northbridge and southbridge chipsets were rearranged. The northbridge is now eliminated completely and its functions, the memory controller and PCI Express lanes for expansion cards, are now incorporated into the CPU die or package.

The PCH then incorporates a few of the remaining northbridge functions (e.g. clocking) in addition to all of the southbridge's functions. The system clock was previously a connection and is now fused in with the PCH. Two different connections exist between the PCH and the CPU: Flexible Display Interface (FDI) and Direct Media Interface (DMI). The FDI is only used when the chipset requires supporting a processor with integrated graphics. The Intel Management Engine was also moved to the PCH starting with the Nehalem processors and 5-Series chipsets.

With the northbridge functions integrated to the CPU, much of the bandwidth needed for chipsets is now relieved.

This style began in Nehalem and will remain for the foreseeable future, through Cannonlake.

Phase-out

Beginning with ultra-low-power Broadwells and continuing with mobile Skylake processors, Intel incorporated the clock, PCI controller, and southbridge IO controllers into the CPU package, eliminating the PCH for a system on a chip (SOC) design. Rather than DMI, these SOCs directly expose PCIe lanes, as well as SATA, USB, and HDA lines from integrated controllers, and SPI/I²C/UART/GPIO lines for sensors. Like PCH-compatible CPUs, they continue to expose DisplayPort, RAM, and SMBus lines. However, a fully integrated voltage regulator will be absent until Cannonlake.

Ibex Peak

The Intel 5 Series chipsets were the first to introduce a PCH. This first PCH is codenamed Ibex Peak.

This has the following variations:

Issues

Langwell

Langwell is the codename of a PCH in the Moorestown MID/smartphone platform. for Atom Lincroft microprocessors.

This has the following variations:

Tiger Point

Tiger Point is the codename of a PCH in the Pine Trail netbook platform chipset for Atom Pineview microprocessors.

This has the following variations:

Topcliff

Topcliff is the codename of a PCH in the Queens Bay embedded platform chipset for Atom Tunnel Creek microprocessors.

It connects to the processor via PCI-E (vs. DMI as other PCHs do).

This has the following variations:

Cougar Point

Cougar Point is the codename of a PCH in Intel 6 Series chipsets for mobile, desktop, and workstation / server platforms. It is most closely associated with Sandy Bridge processors.

This has the following variations:

Issues

In the first month after Cougar Point's release, January 2011, Intel posted a press release stating a design error had been discovered. Specifically, a transistor in the 3 Gbit/s PLL clocking tree was receiving too high voltage. The projected result was a 5–15% failure rate within three years of 3 Gbit/s SATA ports, commonly used for storage devices such as hard drives and optical drives. Through OEMs, Intel plans to repair or replace all affected products at a cost of $700 million.

Whitney Point

Whitney Point is the codename of a PCH in the Oak Trail tablet platform for Atom Lincroft microprocessors.

This has the following variations:

Panther Point

Panther Point is the codename of a PCH in Intel 7 Series chipsets for mobile and desktop. It is most closely associated with Ivy Bridge processors. These chipsets have integrated USB 3.0.

This has the following variations:

Cave Creek

Cave Creek is the codename of the PCH most closely associated with Crystal Forest platforms and Gladden or Sandy Bridge-EP/EN processors.

Patsburg

Patsburg is the codename of a PCH in Intel 7 Series chipsets for server and workstation using the LGA 2011 socket. It was initially launched in 2011 as part of Intel X79 for the desktop enthusiast Sandy Bridge-E processors in Waimea Bay platforms. Patsburg was then used for the Sandy Bridge-EP server platform (the platform was codenamed Romley and the CPUs codenamed Jaketown, and finally branded as Xeon E5-2600 series) launched in early 2012.

Launched in the fall of 2013, the Ivy Bridge-E/EP processors (the latter branded as Xeon E5-2600 v2 series) also work with Patsburg, typically with a BIOS update.

Patsburg has the following variations:

Coleto Creek

Coleto Creek is the codename of the PCH most closely associated with Highland Forest platforms and Ivy Bridge-EP processors.

Lynx Point

Lynx Point is the codename of a PCH in Intel 8 Series chipsets, most closely associated with Haswell processors with LGA 1150 socket. The Lynx Point chipset connects to the processor primarily over the Direct Media Interface (DMI) interface.

The following variants are available:

In addition the following newer variants are available, additionally known as Wildcat Point, which also support Haswell Refresh processors:

Issues

A design flaw causes devices connected to the Lynx Point's integrated USB 3.0 controller to be disconnected when the system wakes up from the S3 state (Suspend to RAM), forcing the USB devices to be reconnected although no data is lost. This issue is corrected in C2 stepping level of the Lynx Point chipset.

Wellsburg

Wellsburg is the codename for the C610-series PCH, supporting the Haswell-E (Core i7 Extreme), Haswell-EP (Xeon E5-16xx v3 and Xeon E5-26xx v3), and Broadwell-EP (Xeon E5-26xx v4) processors. Generally similar to Patsburg, Wellsburg consumes only up to 7 W when fully loaded.

Wellsburg has the following variations:

Sunrise Point

Sunrise Point is the codename of a PCH in Intel 100 Series chipsets, most closely associated with Skylake processors with LGA 1151 socket.

The following variants are available: