L1 cache 64 KB per core L3 cache 4 MB to 24 MB shared Created November 2008 | L2 cache 256 KB per core Model Core Series Transistors 731M 45 nm (C0, D0) | |

| ||

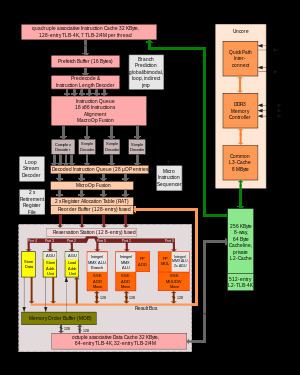

Nehalem microarchitecture

Nehalem /nəˈheɪləm/ is the codename for an Intel processor microarchitecture, which is the successor to the older Core microarchitecture. A preview system with two Nehalem processors was shown at Intel Developer Forum in 2007, and the first processor released with the Nehalem architecture was the desktop Core i7, which was released in November 2008. The first generation of the Intel Core series of processors, Nehalem designs led to the introduction of Core i7 and i5 models (no Core i3 is based on Nehalem). The subsequent Westmere and Sandy Bridge designs would include Core i3 processors.

Contents

- Nehalem microarchitecture

- Technology

- Performance and power improvements

- Server and desktop processors

- Roadmap

- References

"Nehalem" is a recycled Intel codename and namesake of the Nehalem River. It is an architecture that differs radically from Netburst, while retaining some of the latter's minor features. Nehalem-based microprocessors use the 45 nm process, run at higher clock speeds, and are more energy-efficient than Penryn microprocessors. Hyper-threading is reintroduced, along with a reduction in L2 cache size, as well as an enlarged L3 cache that is shared among all cores.

Nehalem was replaced with the Sandy Bridge microarchitecture, released in January 2011.

Technology

Performance and power improvements

It has been reported that Nehalem has a focus on performance, thus the increased core size. Compared to Penryn, Nehalem has:

Overclocking is possible with Bloomfield processors and the X58 chipset. Lynnfield processors use a PCH removing the need for a northbridge.

Nehalem processors incorporate SSE 4.2 SIMD instructions, adding seven new instructions to the SSE 4.1 set in the Core 2 series. The Nehalem architecture reduces atomic operation latency by 50% in an attempt to eliminate overhead on atomic operations such as the LOCK CMPXCHG compare-and-swap instruction.

Server and desktop processors

Roadmap

The successor to Nehalem and Westmere is Sandy Bridge.