| ||

HRS-100, ХРС-100, GVS-100 or ГВС-100, (see Ref.#1, #2, #3 and #4) (Serbian: Hibridni Računarski Sistem, Russian: Гибридная Вычислительная Система, English: Hybrid Computer System) was a third generation hybrid computer developed by Mihajlo Pupin Institute (Serbia, then SFR Yugoslavia) and engineers from USSR in the period from 1968. to 1971. Three systems HRS-100 were deployed in Academy of Sciences of USSR in Moscow and Novosibirsk ( Akademgorodok) in 1971 and 1978. More production was contemplated for use in Czechoslovakia and German Democratic Republic (DDR), but that was not realised.

Contents

- Overview

- Central processing unit

- Primary memory

- Secondary storage

- Peripherals

- Interconnection hardware

- Analog computer

- Development team

- References

HRS-100 was invented and developed to study the dynamical systems in real and accelerated scale time and for efficient solving of wide array of scientific tasks at the institutes of the A.S. of USSR (in the fields: Aerospace-nautics, Energetics, Control engineering, Microelectronics, Telecommunications, Bio-medical investigations, Chemical industry etc.).

Overview

HRS-100 was composed of:

Central processing unit

HRS-100 has a 32-bit TTL MSI processor with following capabilities:

Primary memory

Primary memory was made up of 0.9 μs cycle time magnetic core modules. Each 36-bit word is organized as follows:

Secondary storage

Secondary storage was composed of up to 8 of the CDC 9432D removable-media disk drive devices. Capacity of one set of disk platters was about 4 million 6-bit words or 768,000 words of HRS-100 computer. Total, combined, capacity of 8 drives is, therefore, 6,144,000 words. Each disk set comprised 6 platters out of which 10 surfaces are used. Data was organized into 100 cylinders and 16 1536-bit sectors (48 HRS-100 words).

Average data access time was 100 ms (max. 165 ms). Maximum seek time was 25 ms. Raw transfer sector write speed was 208,333 characters/s.

Peripherals

Peripherals communicate with the computer using interrupts and full length of HRS-100 words. Each separate unit has its own controller. Following devices were produced or planned:

Interconnection hardware

Interconnection hardware (called simply "Link") connects digital and analog components of HRS-100 into a single unified computer. It comprised:

Link takes commands from a digital computer component and organizes their execution via 2 32-bit data channels, 11 control channels, synchronization signals via 3 channels and 9 interrupt channels. Connection between a digital and analog computers is established through a "common-control panel" and two separate consoles. Communicating digital data with analog consoles is done through 16 control, 16 sensitivity, 16 indicator and 10 functional "lines".

Analog-to-digital conversion is achieved by a single signed 14-bit 70,000 samples/s A/D converter and a 32-channel multiplexer. Digital-to-analog conversion is achieved by 16 independent signed 14-bit D/A converters with double registers. Typical D/A conversion took 2 μs.

Analog computer

Analog component of HRS-100 system is composed of up to seven analog machines all connected to the common-control panel. It contains all elements required to independently solve linear and non-linear differential equations, both directly and iteratively.

Units of analog computer:

Linear analog computer elements were designed to facilitate 0.01% precision in static mode and 0.1% in dynamic mode, for signals up to 1kHz. Non-linear elements precision was not required to be better than 0.1%.

Analog component of HRS-100 has its own peripheral units:

Development team

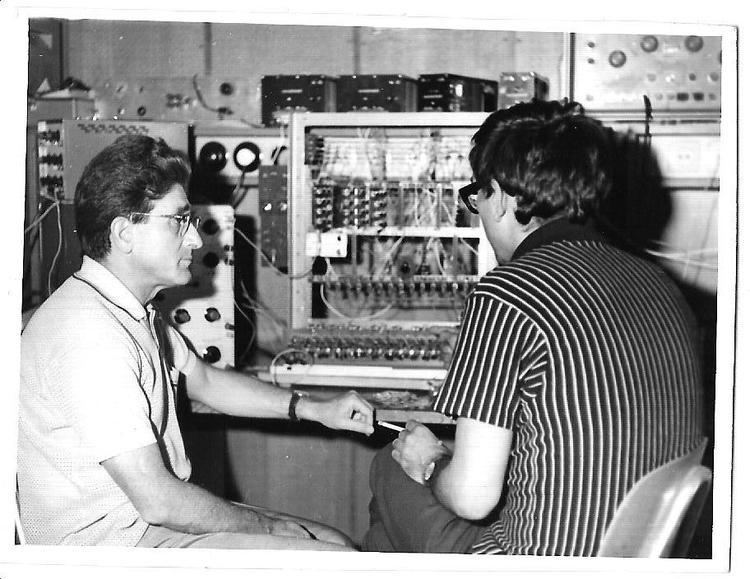

HRS-100 was designed and developed by the following team (see Ref.#1, #4, #5, and #6):