| ||

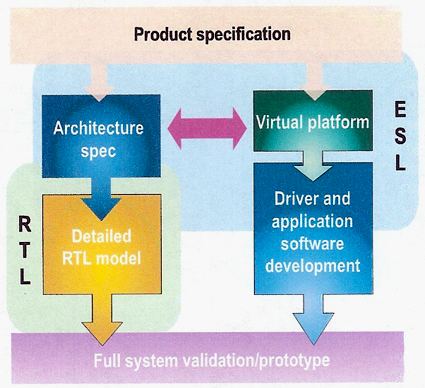

Electronic system level (ESL) design and verification is an electronic design methodology, focused on higher abstraction level concerns. The term Electronic System Level or ESL Design was first defined by Gartner Dataquest, an EDA-industry-analysis firm, on February 1, 2001. It is defined in ESL Design and Verification as: "the utilization of appropriate abstractions in order to increase comprehension about a system, and to enhance the probability of a successful implementation of functionality in a cost-effective manner."

Contents

The basic premise is to model the behavior of the entire system using a high-level language such as C, C++, LabVIEW, or MATLAB or using graphical "model-based" design tools. Newer languages are emerging that enable the creation of a model at a higher level of abstraction including general purpose system design languages like SysML as well as those that are specific to embedded system design like SMDL and SSDL. Rapid and correct-by-construction implementation of the system can be automated using EDA tools such as high-level synthesis and embedded software tools, although much of it is performed manually today. ESL can also be accomplished through the use of SystemC as an abstract modeling language.

Electronic System Level is an established approach at many of the world’s leading System-on-a-chip (SoC) design companies, and is being used increasingly in system design. From its genesis as an algorithm modeling methodology with ‘no links to implementation’, ESL is evolving into a set of complementary methodologies that enable embedded system design, verification, and debugging through to the hardware and software implementation of custom SoC, system-on-FPGA, system-on board, and entire multi-board systems.

Design and verification are two distinct disciplines within this methodology. Some practices are to keep the two elements separate, while others advocate for closer integration between design and verification.

Design

Whether ESL or other systems, design refers to "the concurrent design of the hardware and software parts of an electronic product."

Verification

In ESL design and verification, verification testing is used to prove the integrity of the design of the system or device. Numerous verification techniques may be applied; these test methods are usually modified or customized to better accommodate the system or device under test. Common ESL verification methods include, but are not limited to:

Verification is often provided by the system/device designer, but in many instances, additional independent verification is required

Challenges and criticism

Some criticisms of ESL design and verification have been raised. These include too much focus on C-based languages and challenges in representing parallel processes. It can also be argued that ESL design and verification is a subset of verification and validation.