Designed by ARM Holdings Microarchitecture ARMv7-A | Max. CPU clock rate 1.0 GHz to 2.5 GHz | |

| ||

Produced In production late 2011, to market late 2012 Min. feature size 32 nm/28 nm initially to 22 nm roadmap Cores 1–4 per cluster, 1–2 clusters per physical chip | ||

The ARM Cortex-A15 MPCore is a 32-bit processor core licensed by ARM Holdings implementing the ARMv7-A architecture. It is a multicore processor with out-of-order superscalar pipeline running at up to 2.5 GHz.

Contents

Overview

ARM has claimed that the Cortex-A15 core is 40 percent more powerful than the Cortex-A9 core with the same number of cores at the same speed. The first A15 designs came out in the autumn of 2011, but products based on the chip did not reach the market until 2012.

Key features of the Cortex-A15 core are:

Chips

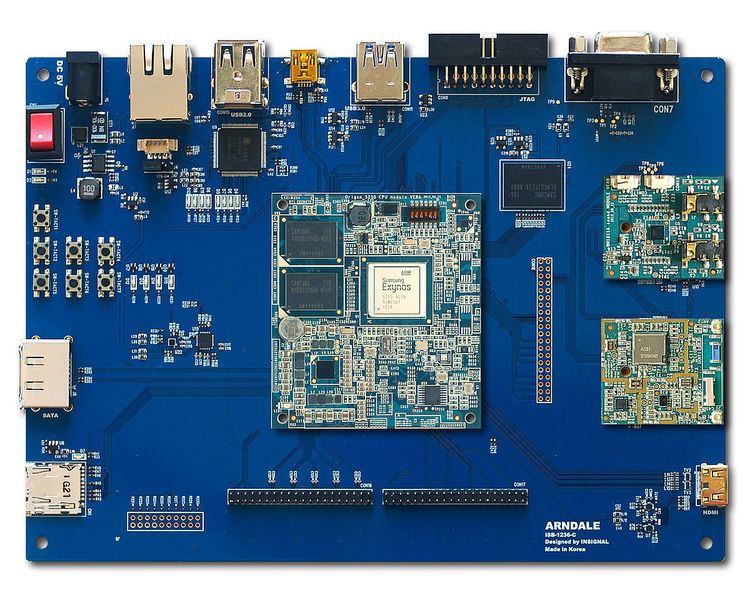

First implementation came from Samsung in 2012 with the Exynos 5 Dual, which shipped in October 2012 with the Samsung Chromebook Series 3 (ARM version), followed in November by the Google Nexus 10.

Press announcements of current implementations:

Other licensees, such as LG, are expected to produce an A15 based design at some point.