1 ... 5 ... 6 5 | 3 ... 7 6 5 4 | |

| ||

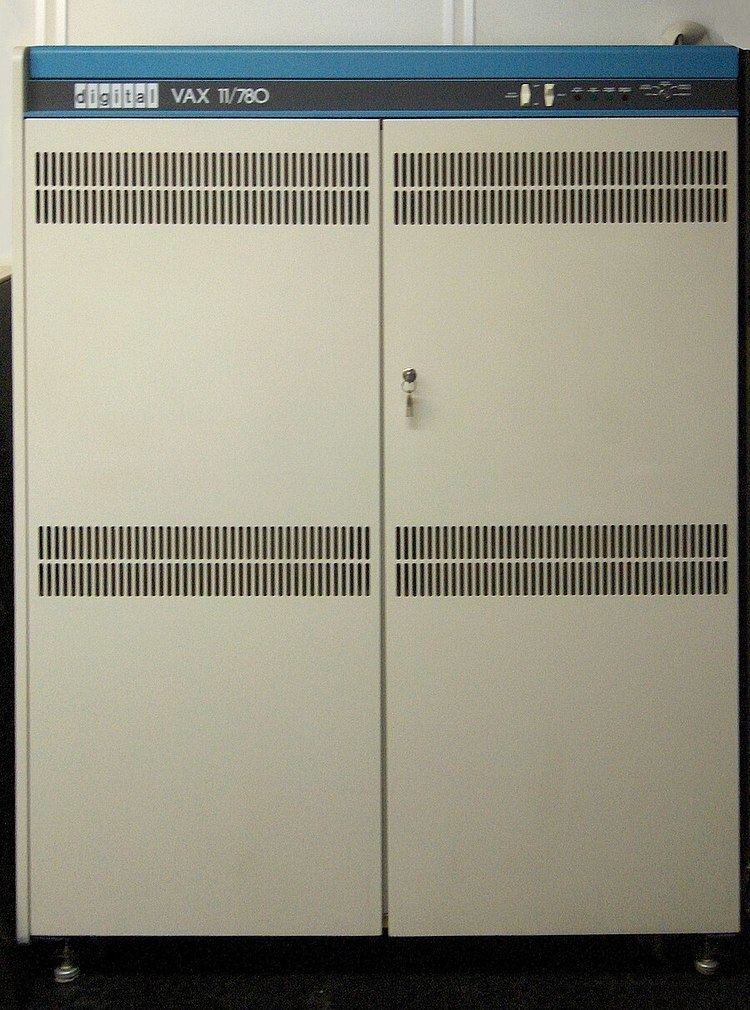

The VAX-11 was a family of minicomputers developed and manufactured by Digital Equipment Corporation (DEC) using processors implementing the VAX instruction set architecture (ISA). The VAX-11/780 was the first VAX computer.

Contents

VAX-11/780

The VAX-11/780, code-named "Star", was introduced on 25 October 1977 at DEC's Annual Meeting of Shareholders. It was the first computer to implement the VAX architecture. The VAX-11/780 central processing unit (CPU) was built from transistor-transistor logic (TTL) devices and had a 200 ns cycle time (5 MHz) and a 2 kB cache. Memory and I/O were accessed via the Synchronous Backplane Interconnect (SBI).

The VAX-11/780 supported 128 kB to 8 MB of memory (2 MB initially) through one or two memory controllers. Each memory controller supported 128 kB to 4 MB of memory. The memory was constructed from 4 or 16 kbit metal oxide semiconductor (MOS) RAM chips mounted on memory array cards. Each memory controller controlled up to 16 array cards. The memory was protected by error correcting code (ECC).

The VAX-11/780 used the Unibus and Massbus for I/O. Unibus was used for attaching peripherals and Massbus for disk and tape drives. Both buses were provided by adapters that interfaced the bus to the SBI. All systems came with one Unibus as standard, with up to four supported. Massbus was optional, with up to four supported. The VAX-11/780 also supported Computer Interconnect (CI), a proprietary network to attach disk drives and potentially share them with other VAX computers. Later, this feature was used to connect VAX computers in a VMScluster.

VAX-11/782

The VAX 11/782, code-named "Atlas", was a dual-processor VAX-11/780 introduced in 1982. Both processors shared the same MA780 multiport memory bus and the system operated asymmetrically with the primary CPU performing all I/O operations and process scheduling with the second, attached processor only used for additional computationally-intensive work. For multistream computation-intensive tasks the system delivered up to 1.8 times the performance of a VAX 11/780.

VAX-11/785

The VAX-11/785, code-named "superstar", was introduced in April 1984. It was essentially a faster VAX-11/780, with a CPU cycle time of 133 ns (7.52 MHz) versus the 200 ns (5 MHz) CPU cycle time of the VAX-11/780. The memory subsystem was also upgraded to support higher capacity memory boards.

VAX-11/787

The VAX-11/787 was a dual-processor variant of the VAX-11/785.

VAX-11/750

The VAX-11/750, code-named "Comet", was a more compact, lower-performance TTL gate array–based implementation of the VAX architecture introduced in October 1980. The CPU had a 320 ns cycle time (3.125 MHz).

VAX-11/751

A ruggedized rack-mount VAX-11/750.

VAX-11/730

Introduced in April 1982, the VAX-11/730, code-named "Nebula", was a still-more-compact, still-lower-performance bit slice implementation of the VAX architecture. Its CPU had a 270 ns cycle time (3.70 MHz).

VAX-11/725

Code-named "LCN" ("Low-Cost Nebula"), it was a cost-reduced model of the VAX-11/730. Its CPU had a 270 ns cycle time (3.70 MHz).

VAX 11/788

The VAX-11/788 was code-named "VISQ".

Remaining machines

The Living Computer Museum of Seattle, Washington maintains a VAX-11/780-5 (field-upgraded VAX-11/780) running OpenVMS 6.2, which is available to interested parties via telnet. The Computer History Museum of Mountain View, California has three VAX-11/780 systems, one VAX-11/725, one VAX-11/730, and one VAX-11/750 within its permanent collection.