| ||

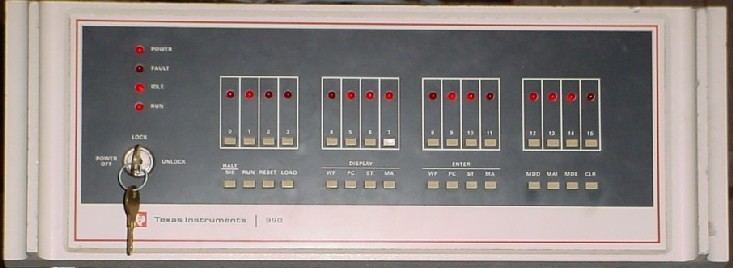

The TI-990 was a series of 16-bit minicomputers sold by Texas Instruments (TI) in the 1970s and 1980s. The TI-990 was a replacement for TI's earlier minicomputer systems, the TI-960 and the TI-980. It had several uniquely innovative features, and was easier to program than its predecessors.

Contents

Workspaces

The TI-990 had a unique concept that registers are stored in memory and are referred to through a hard register called the Workspace Pointer. The concept behind the workspace is that main memory was based on the new semiconductor RAM chips that TI had developed and ran at the same speed as the CPU. This meant that it didn't matter if the "registers" were real registers in the CPU or represented in memory. When the Workspace Pointer is loaded with a memory address, that address is the origin of the "registers".

There are three hard registers in the 990; the Workspace Pointer (WP), the Program Counter (PC) and the Status register (ST). A context switch entailed the saving and restoring of only the hard registers.

Extended Operation

The TI-990 had a facility to allow extended operations through the use of plug in hardware. If the hardware is not present the CPU traps to allow software to perform the function. The operation code (XOP) allowed for 15 attached devices on a system. Although, device 15 is reserved, by convention, to be used as the systems call entry for user programs to request systems services.

Instruction set

Programmers liked the TI-990 design because it had a fairly orthogonal instruction set which allowed a programmer to separately memorize all of the operations and the methods of accessing operands.

The basic instruction formats allowed for one, two and three word instructions. The model 990/12 CPU allowed for a four word instruction with the extended mode operations.

General register addressing modes

(R is a general register, 0 to 15.)

0. Register - the value is to or from a register: OPR R ; R contains operand1. Indirect register - register is used as a memory address to read or write: OPR *R ; R contains address2. Indexed: OPR @MEM(R); R contains index value, R0 is not used in indexing and allows direct memory addressing3. Autoincrement: OPR *R+ ; R contains address of address, then increment R by the length of the operand typeSeveral registers had special usages that reserve their use, the register and their usages are:

TI-990 instructions

The 990/4, 990/5, 990/9 instruction sets consisted of 69 instructions, the 990/10 had 72 instructions, the 990/10A had 77 instructions and the 990/12 had 144 instructions. The instructions are divided into types that have similar characteristics.

The first part of the word specifies the operation to be performed, the remaining two parts provide information for locating the operands.

The first part of the word specifies the operation to be performed, the second part is a relative offset to where to go, for JMP instructions, or the relative offset for CRU bit addressing.

One part of the word specifies the operation, the second part provides the register, the third part provides information for locating the second operand.

The first part of the word specifies the operation to be performed, the second part is the bit width of the operation, the third part provides information for locating the second operand.

The first part of the word specifies the operation to be performed, the second part is the shift count, the third part specifies the register to shift.

The first part specifies the operation to be performed, the second part provides information for locating the second operand.

The word specified the operation to be performed.

The first part specifies the operation, the second part specifies the register or mask. The third part, if present, specifies an immediate operand in a second word.

One part of the word specifies the operation, the second part provides the register, the third part provides information for locating the second operand.

The first part specifies the operation, the second part specifies the map file (0=kernel, 1=user) and the third specifies a register. This instruction supported on the 990/10, 990/10A and 990/12.

The first word is the opcode; the first part of the second word is the byte count field, the second part is the destination operand and the third part is the source operand. These instructions supported on the 990/12.

The first part of the first word is the opcode, the second part of the first word indicates a checkpoint register; the first part of the second word is the byte count field, the second part is the destination operand and the third part is the source operand. These instruction supported on the 990/12.

The first word is the opcode; the first part of the second word is the byte count field, the second part is the shift count and the third part is the source operand. These instructions supported on the 990/12.

The first word is the opcode; the first part of the second word is the position field and the second part is the source operand. These instructions supported on the 990/12.

The first part of the first word is the opcode, the second part of the first word indicates a width; the first part of the second word is the position, the second part is the source operand. This instruction supported on the 990/12.

The first part of the first word is the opcode, the second part of the first word indicates a width; the first part of the second word is the position, the second part is the destination operand and the third part is the source operand. These instructions supported on the 990/12.

The first word is the opcode; the first part of the second word is the value field and the second part is the register and the third part is the relative offset. These instructions supported on the 990/12.

The first part of the word is the opcode and the second part is the register specification. These instructions supported on the 990/12.

The first word is the opcode; the first part of the second word is the destination operand and the second part is the source operand. This instruction supported on the 990/12.

The first word is the opcode; the first part of the second word is the condition code field, the second part is the destination operand and the third part is the source operand. These instructions supported on the 990/12.

The first part of the first word is the opcode, the second part of the first word specifies the destination length; the first part of the second word specifies the source length, the second part is the destination operand and the third part is the source operand. This instruction supported on the 990/12.

Assembly Language Programming Example

A complete "Hello, world!" program in TI-990 assembler, to run under DX10:

IDT 'HELLO' TITL 'HELLO - hello world program'* DXOP SVC,15 Define SVCTMLUNO EQU 0 Terminal LUNO*R0 EQU 0R1 EQU 1R2 EQU 2R3 EQU 3R4 EQU 4R5 EQU 5R6 EQU 6R7 EQU 7R8 EQU 8R9 EQU 9R10 EQU 10R11 EQU 11R12 EQU 12R13 EQU 13R14 EQU 14R15 EQU 15* DATA WP,ENTRY,0* * Workspace (On the 990 we can "preload" registers)*WP DATA 0 R0 DATA 0 R1 DATA >1600 R2 - End of program SVC DATA >0000 R3 - Open I/O opcode DATA >0B00 R4 - Write I/O opcode DATA >0100 R5 - Close I/O opcode DATA STRING R6 - Message address DATA STRLEN R7 - Message length DATA 0 R8 DATA 0 R9 DATA 0 R10 DATA 0 R11 DATA 0 R12 DATA 0 R13 DATA 0 R14 DATA 0 R15* * Terminal SVC block*TRMSCB BYTE 0 SVC op code (0 = I/O)TRMERR BYTE 0 Error codeTRMOPC BYTE 0 I/O OP CODETRMLUN BYTE TMLUNO LUNOTRMFLG DATA 0 FlagsTRMBUF DATA $-$ Buffer address TRMLRL DATA $-$ Logical record lengthTRMCHC DATA $-$ Character count* * Message*STRING TEXT 'Hello world!' BYTE >D,>ASTRLEN EQU $-STRING EVEN PAGE* * Main program entry*ENTRY MOVB R3,@TRMOPC Set open opcode in SCB SVC @TRMSCB Open terminal MOVB @TRMERR,R0 Check for error JNE EXIT MOVB R4,@TRMOPC Set write opcode MOV R6,@TRMBUF Set buffer address MOV R7,@TRMLRL Set logical record length MOV R7,@TRMCHC and character count SVC @TRMSCB Write message MOVB @TRMERR,R0 Check for error JNE CLOSECLOSE MOVB R5,@TRMOPC Set close opcode SVC @TRMSCB Close terminalEXIT SVC R2 Exit program* ENDYou can try out the above for yourself on a TI-990 simulator. Dave Pitts's sim990 simulates the TI-990 and includes software kits for native operating systems (including DX10).

The following program is a standalone version that prints on the serial terminal connected to CRU address 0. It illustrates the CRU I/O and workspace linkage for the PRINT subroutine.

IDT 'HELLO' TITL 'HELLO - hello world program'*R0 EQU 0R1 EQU 1R2 EQU 2R3 EQU 3R4 EQU 4R5 EQU 5R6 EQU 6R7 EQU 7R8 EQU 8R9 EQU 9R10 EQU 10R11 EQU 11R12 EQU 12R13 EQU 13R14 EQU 14R15 EQU 15** Terminal CRU bits*TRMCRU EQU >0 Terminal device addressXMIT EQU 8DTR EQU 9RTS EQU 10WRQ EQU 11RRQ EQU 12NSF EQU 13* PAGE** Main program entry*ENTRY LWPI WP Load our workspace pointer BLWP @PRINT Call our print routine DATA STRING DATA STRLEN IDLE*WP BSS 32 Main program workspace** Message*STRING TEXT 'Hello world!' BYTE >D,>ASTRLEN EQU $-STRING EVEN PAGE** Print a message*PRINT DATA PRWS,PRENTPRENT EQU $ MOV *R14+,R2 Get buffer address MOV *R14+,R1 Get message length SBO DTR Enable terminal ready SBO RTSPRI010 LDCR *R2+,8 Send out a character TB WRQ Wait until done JNE $-2 SBZ WRQ DEC R1 JGT PRI010 RTWP*PRWS DATA 0,0,0,0,0,0,0,0 DATA 0,0,0,0,TRMCRU,0,0,0* END ENTRYTI-990 models

The TI-990 processors fell into several natural groups depending on the original design upon which they are based and which I/O bus they used.

All models supported the Communications Register Unit (CRU) which is a serial bit addressable I/O bus. Also, supported on higher end models was the TILINE I/O bus which is similar to DEC's popular UNIBUS. The TILINE also supported a master/slave relationship that allowed multiple CPU boards in a common chassis with arbitration control.

TILINE/CRU models

The following models used the TILINE as their principal mass storage bus:

CRU only models

The following models used the CRU as their principal bus:

Operating systems

Several operating systems were available for the TI-990

From TI:

From third parties: