Produced From 1992 to 1995 Max. CPU clock rate 33 MHz to 90 MHz Cores 1 | ||

| ||

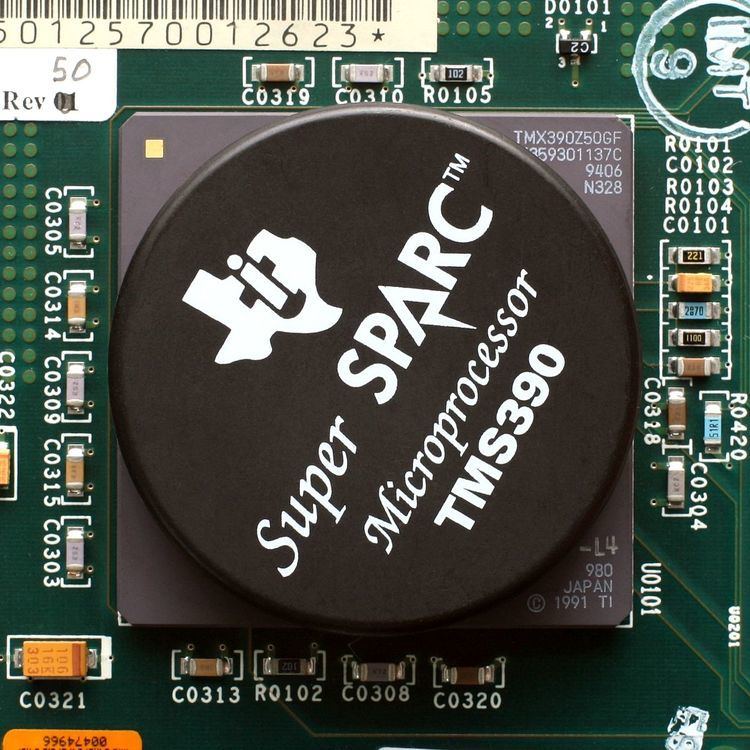

The SuperSPARC is a microprocessor that implements the SPARC V8 instruction set architecture (ISA) developed by Sun Microsystems. 33 and 40 MHz versions were introduced in 1992. The SuperSPARC contained 3.1 million transistors. It was fabricated by Texas Instruments (TI) at Miho, Japan in a 0.8 micrometre triple-metal BiCMOS process.

Contents

There were two derivatives of the SuperSPARC: the SuperSPARC+ and SuperSPARC-II. The SuperSPARC+ was developed to remedy some of the design flaws that limited the SuperSPARC's clock frequency and thus performance. The SuperSPARC-II, introduced in 1994, was a major revision with improvements that enabled the microprocessor to reach 80 MHz in desktop systems and 90 MHz in the more heavily cooled SPARCserver-1000E.

The SuperSPARC-II was replaced in 1995 by the 64-bit UltraSPARC, an implementation of the 64-bit SPARC V9 ISA.