| ||

Phy chip

PHY is an abbreviation for the physical layer of the OSI model and refers to the circuitry required to implement physical layer functions.

Contents

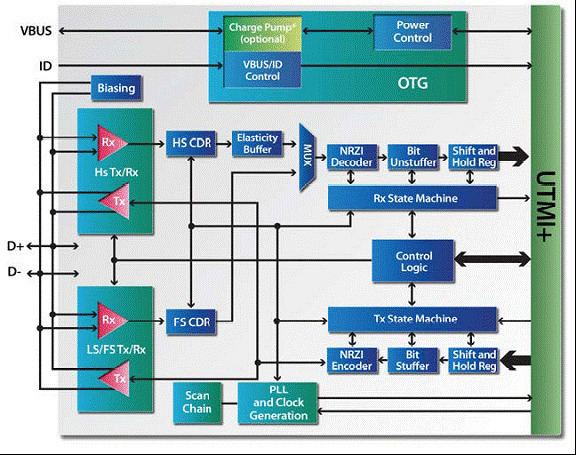

A PHY connects a link layer device (often called MAC as an abbreviation for media access control) to a physical medium such as an optical fiber or copper cable. A PHY device typically includes a Physical Coding Sublayer (PCS) and a Physical Medium Dependent (PMD) layer. The PCS encodes and decodes the data that is transmitted and received. The purpose of the encoding is to make it easier for the receiver to recover the signal.

Example uses

Ethernet physical transceiver

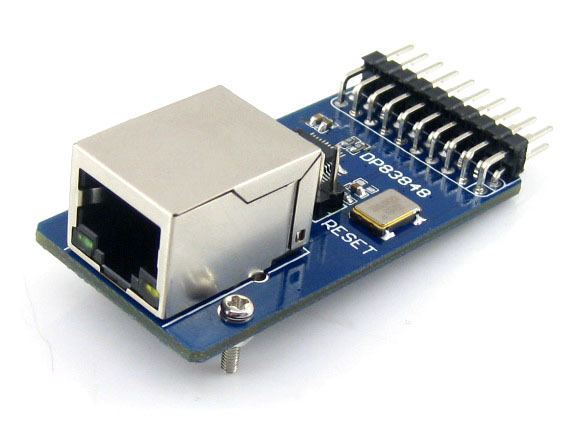

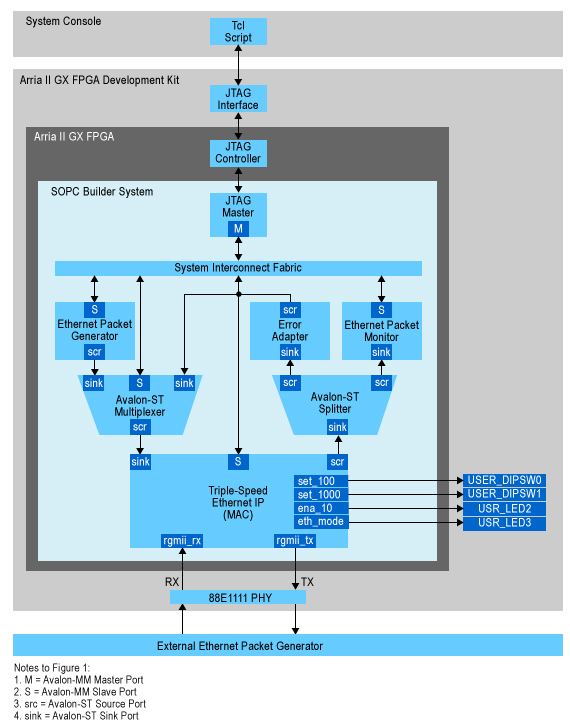

The Ethernet PHY is a component that operates at the physical layer of the OSI network model. It implements the Ethernet physical layer portion of the 1000BASE-T, 100BASE-TX, and 10BASE-T standards.

More specifically, the Ethernet PHY is a chip that implements the hardware send and receive function of Ethernet frames; it interfaces between the analog domain of Ethernet's line modulation and the digital domain of link-layer packet signaling. The PHY usually does not handle MAC addressing, as that is the link layer's job. Similarly, Wake-on-LAN and Boot ROM functionality is implemented in the network interface card (NIC), which may have PHY, MAC and other functionality integrated into one chip or as separate chips.

Examples include the Vitesse Semiconductor SimpliPHY and SynchroPHY VSC82xx/85xx/86xx family and Marvell Alaska 88E1310/88E1310S/88E1318/88E1318S Gigabit Ethernet transceivers.

An Ethernet physical transceiver can also be referred to as a physical layer transmitter and/or receiver, a physical layer transceiver, a PHY transceiver, a PHYceiver, or simply a PHY. The term PHYceiver is often shown as being TM (Trade Marked) but is not currently registered with TESS United States Patent and Trademark Office.