Produced 2010 FSB speeds 2 Gbps | Designed by MCST Max. CPU clock rate 750 MHz to 1 GHz Min. feature size 100 mm² | |

| ||

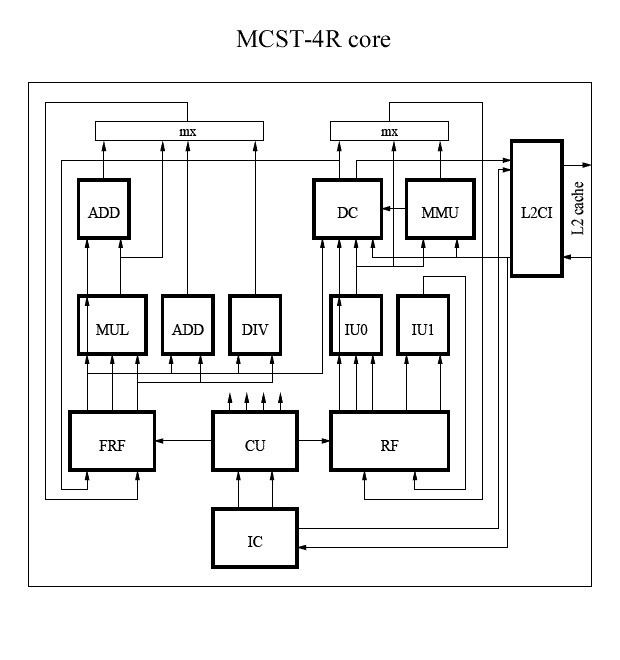

The MCST R1000 (Russian: МЦСТ R1000) is a 64-bit microprocessor developed by Moscow Center of SPARC Technologies (MCST) and fabricated by TSMC.

During development this microprocessor was designated as MCST-4R.

MCST R1000 Highlights

References

MCST-R1000 Wikipedia(Text) CC BY-SA