| ||

The EISC (Extendable Instruction Set Computer) is a compressed code processor architecture for embedded applications. It has both the properties of RISC architecture, simplicity, and that of CISC processor, expandability. The architecture is developed by Advanced Digital Chips Inc., Seoul, Korea.<http://www.adc.co.kr>

Contents

Introduction

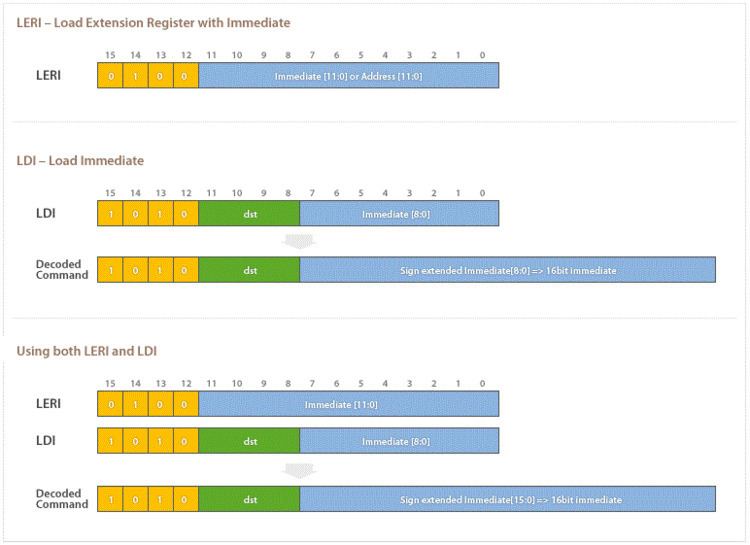

EISC stands for "Extendable Instruction Set Computer". EISC processor advantages over existing CISC and RISC architectures: EISC can represent any length of an operand without variable length instruction elimination inefficiencies caused by difficulties in processing variable instruction decoding. EISC architecture maximized cost and performance efficiency and at the same time offers flexibility and power through the Extendable Register and Extension Flag, which increase the code density while allowing a simple 16-bit-based instruction set.

Extension (Extension Register (ER) and Extension Flag (E))

EISC has Extension Register (ER) and Extension Flag (E) for variable-length operand.

Instruction Set Architecture Family

The EISC has 16-bit, 32-bit and 64-bit instruction set architecture family. There exist SE (simple EISC) series and AE (Advanced EISC) series.