| ||

In personal computer microprocessor architecture, a back-side bus (BSB), or backside bus, is a computer bus used to connect the CPU to CPU cache memory, usually L2. If a design utilizes it along with a front-side bus (FSB), it is said to use a dual-bus architecture, or in Intel's terminology Dual Independent Bus (DIB) architecture.

History

BSB is an improvement over the older practice of using a single system bus, because a single bus typically became a severe bottleneck as CPUs and memory speeds increased. Due to its dedicated nature, the back-side bus can be optimized for communication with cache, thus eliminating protocol overheads and additional signals that are required on a general-purpose bus. Furthermore, since a BSB operates over a shorter distance, it can typically operate at higher clock speeds, increasing the computer's overall performance.

Cache connected with a BSB was initially external to the microprocessor die, but now is usually on-die. In the latter case, the BSB clock frequency is typically equal to the processor's, and the back-side bus can also be made much wider (256-bit, 512-bit) than either off-chip or on-chip FSB.

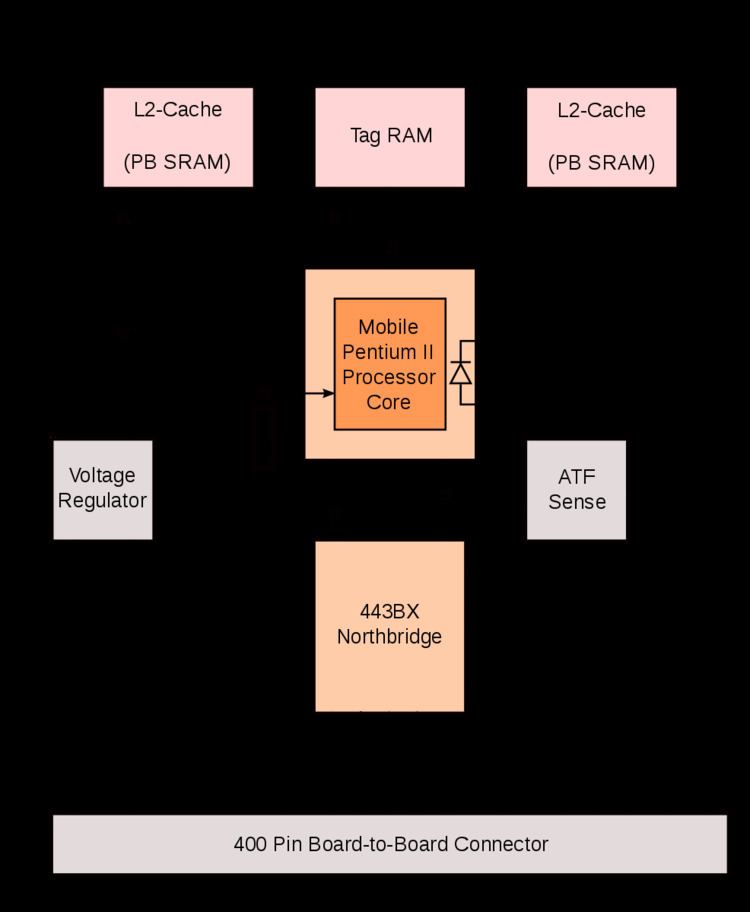

The dual-bus architecture was used in a number of designs, including the IBM and Freescale (formerly the semiconductor division of Motorola) PowerPC processors (certain PowerPC 604 models, the PowerPC 7xx family, and the Freescale 7xxx line), as well as the Intel Pentium II processor, which used it to access their L2 cache (earlier Intel processors accessed the L2 cache over the FSB, while later processors moved it on-chip).