Produced From 2012 to present Designed by IBM, Nintendo IRD, NTD Max. CPU clock rate 1.243 GHz | Marketed by Nintendo Common manufacturer(s) IBM Min. feature size 45 nm | |

| ||

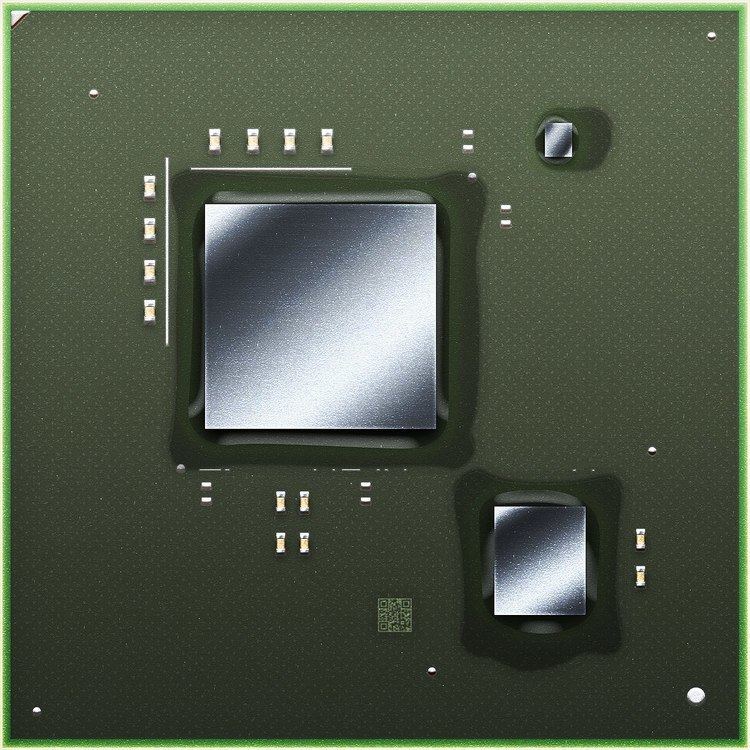

Espresso is the codename of the 32-bit central processing unit (CPU) used in Nintendo's Wii U video game console. It was designed by IBM, and is currently being produced using a 45 nm Silicon on insulator process. The Espresso chip resides together with a GPU from AMD on a MCM manufactured by Renesas. It was revealed at E3 2011 in June 2011 and released in November 2012.

Contents

Design

IBM and Nintendo have revealed that the Espresso processor is a Power Architecture based microprocessor with three cores on a single chip to reduce power consumption and increase speed. The CPU and the graphics processor are placed on a single substrate as a multi-chip module (MCM) to reduce complexity, increase the communication speed between the chips, further reduce power consumption and reduce cost and space required. The two chips were assembled to the complete MCM by Renesas in Japan. Espresso itself is manufactured by IBM in its 300 mm plant in East Fishkill, New York, using 45 nm SOI-technology and embedded DRAM (eDRAM) for caches.

While unverified by Nintendo, hackers, teardowns, and unofficial informants have since revealed more information about the Espresso, such as its name, size and speed. The microarchitecture seems to be quite similar to its predecessors the Broadway and Gekko, i.e. PowerPC 750 based, but enhanced with larger and faster caches and multiprocessor support.

Rumors that the Wii U CPU was derived from IBM's high end POWER7 server processor proved false. Espresso shares some technology with POWER7, such as eDRAM and Power Architecture, but those are superficial similarities.

Specifications

The following specifications have not been officially confirmed by either Nintendo or IBM. They have been obtained by reverse engineering by hacker Hector Martin, who goes by the alias marcan.