| ||

The J-11 is a microprocessor chip set that implements the PDP-11 instruction set architecture (ISA) jointly developed by Digital Equipment Corporation and Harris Semiconductor. It was a high-end chip set designed to integrate the performance and features of the PDP-11/70 onto a handful of chips. It was used in the PDP-11/73, PDP-11/83 and Professional 380.

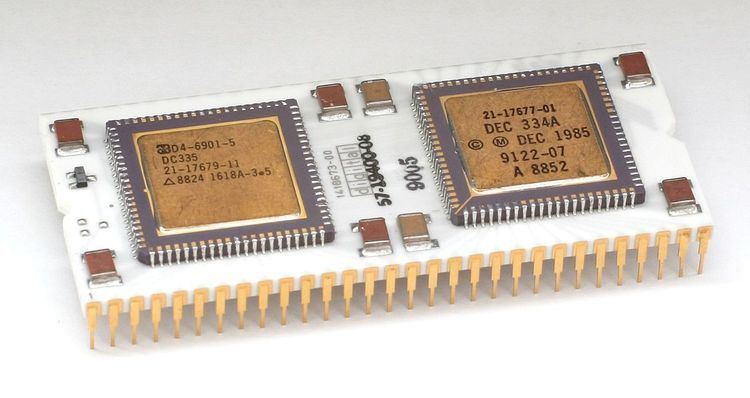

It consisted of a data path chip and a control chip in ceramic leadless packages mounted on a single ceramic hybrid DIP package. The control chip incorporated a control sequencer and a microcode ROM. An optional separate floating-point acclerator (FPA) chip could be used, and was packaged in a standard DIP. The data path chip and control chip were fabricated by Harris in a CMOS process while the FPA was fabricated by Digital in their "ZMOS" NMOS process.

The design originally was intended to support multiple control chips to allow implementation of additional instructions such as the Commercial Instruction Set (CIS), but no such control chips were ever offered.

A clone of the J-11 was manufactured in the Soviet Union under the designation KN1831VM1 (Russian: КН1831ВМ1).