| ||

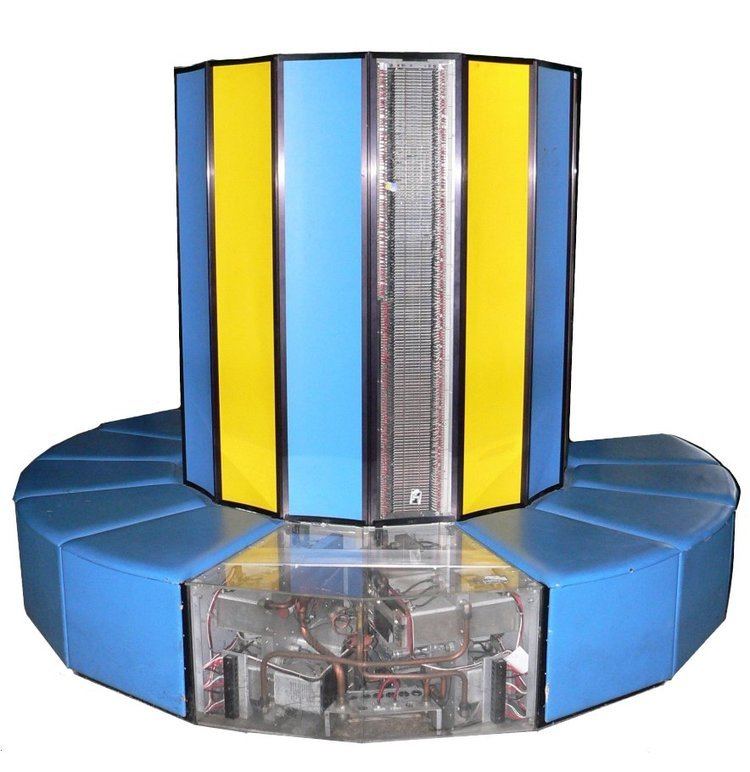

The Cray XMT (codenamed Eldorado) is the third generation of the Cray MTA supercomputer architecture originally developed by Tera. The earlier generations were called the Cray MTA and the Cray MTA-2. The XMT makes the MTA's multithreaded processors, now dubbed Threadstorm, compatible with the 1207-pin Socket F used by AMD Opteron processors. The Threadstorm processors are plugged into systems otherwise identical to the Cray XT4.

The primary advantage of these processors come from efficiency masking memory access time. In a simplified model, at each clock cycle an instruction from one of the threads is executed and another memory request is queued with the understanding that by the time the next round of execution is ready the requested data has arrived. This is contrast to many conventional architectures which stall on memory access. The architecture excels in data walking schemes where subsequent memory access cannot be easily predicted and thus wouldn't be well suited to a conventional cache model.

The Threadstorm processors only execute user code, on top of a simple BSD Unix-based microkernel called MTX; system I/O is performed by Opteron processors running Linux. This third generation MTA system improves clock speed from 220 MHz to 500 MHz, the maximal processor count from 256 to 8192, and maximum memory to 512 TB.

The architecture has been reworked in CPUs such as Threadstorm4, which is used by the XMTs technological successor: Cray's Urika line of big data appliances. Currently, the future of the line is unclear due to competition from commodity processors such as Intel's Xeon.